-

当前位置:芯师爷

- 首页

- 热点资讯

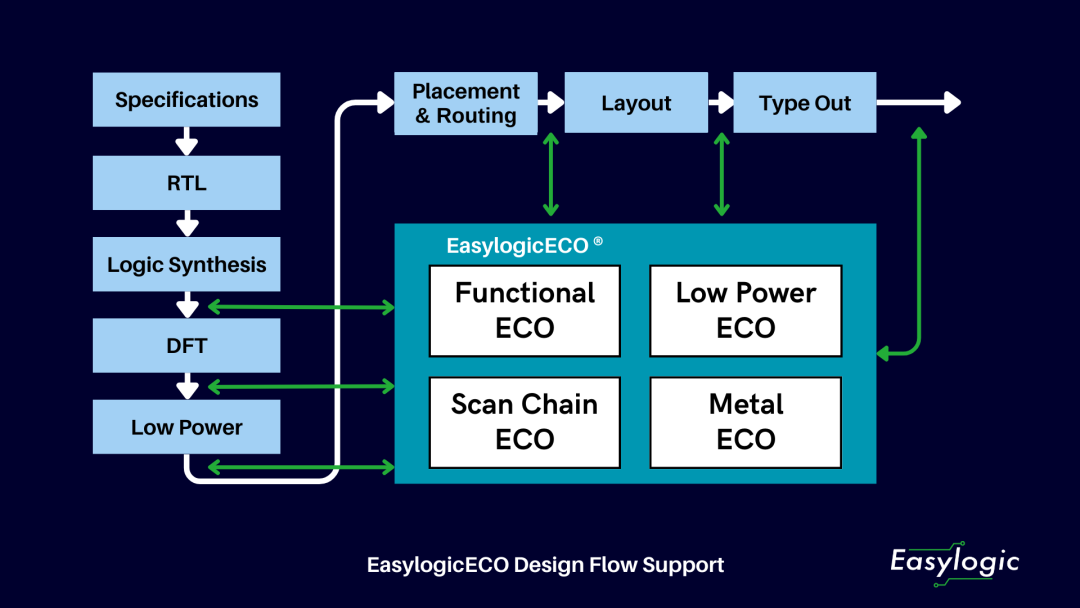

由芯师爷主办的“2023硬核芯”评选活动火热进行中,现以“云展览”的方式为您全方位展示中国芯产品及企业。 诚邀您为中国芯的前进投下宝贵的一票! 扫码查看更多芯企业 奇捷科技(深圳)有限公司 参评奖项 2023年度EDA产品 2023年度卓越成长表现企业 2023年度创业团队 企业介绍 奇捷科技是一家专注于开发电子设计自动化(EDA)工业软件的高科技公司。一直以来,公司从“为功能性ECO创建颠覆性算法”出发,秉承“客户信赖、技术领先、服务至上”的品牌理念,旨在应用Functional ECO的技术为ASIC设计业界提供突破性的设计流程。 公司集结了国内外学术与产业精英,目前在深圳、北京、香港均有研发中心。奇捷科技技术研发成果卓著,推出的商业化工具EasylogicECO,采用了革新的流程与核心算法,与传统工具比,自动化程度大大提高,可以快速生成最小最优化的补丁逻辑,除了可以满足RTL的逻辑功能改动外,同时还可以兼顾其他设计要求,如支持扫描链拼接更新、保持低功耗设计约束、生成补丁考虑物理实现时的时钟树和布线延迟等。 测试结果显示,EasylogicECO的运行时间可比传统工具快数倍,生成的补丁质量比传统工具的结果平均要好30%,有些case甚至能优于同类产品10倍以上,能快速有效地帮助设计团队在最短时间内完成ECO任务,缩短产品开发周期,节省成本。目前已有超20家国内外知名IC设计公司成为了付费用户,服务的商业客户遍布中国大陆、中国台湾、美国、韩国等多个国家和地区。 企业官网 www.easylogiceda.com 产品介绍 产品一 EasylogicECO工具 产品概述 奇捷科技推出的商业化工具EasylogicECO,目前已有超20家国内外知名IC设计公司成为了付费用户。EasylogicECO采用了革新的流程与核心算法,与传统工具比,自动化程度大大提高,可以快速生成最小最优化的补丁逻辑,除了可以满足RTL的逻辑功能改动外,同时还可以兼顾其他设计要求,如支持扫描链拼接更新、保持低功耗设计约束、生成补丁考虑物理实现时的时钟树和布线延迟等。测试结果显示,EasylogicECO的运行时间可比传统工具快数倍,生成的补丁质量比传统工具的结果平均要好30%,有些case甚至能优于同类产品10倍以上。 产品性能 EasylogicECO得到的补丁结果平均要优于市场同类工具30%,对于一些特别案例,结果甚至要优于同类产品10倍以上,同时EasylogicECO直接加入到用户原有的 ASIC 设计流程,与原有工具链无缝衔接。 价格竞争力 和同类产品同一个水平的价格,我们能处理的问题比同类产品多一倍,且响应速度更快,EasylogicECO可处理functional,scan chain, low power以及metal ECO,其中scan chain, low power是其他同类型产品暂时无法处理的。 技术创新 EasylogicECO采用了独创的全自动算法和全新的设计流程,可以大大提高自动化程度,改进补丁结果质量,填补了国内数字前端EDA工具的空白。 客户服务 奇捷科技目前已服务超20家商业客户,遍布中国大陆、中国台湾、美国、韩国等多个国家和地区,拥有完善的现场服务技术支持和售后服务团队,及时响应客户的各种需求,客户一旦遇到任何问题,都可立即联系并获得FAE或RD的帮助,点对点服务,同时提供最快速的定制化支持,客户提出特殊需求,奇捷RD团队会在尽可能短的时间内实现该功能,并及时给予客户新的版本来解决问题,从而使得客户能够在最短时间内完成ECO任务,尽最大努力保证产品研发进度。 案例介绍 针对7nm (超过30亿逻辑门的数字IC设计)AI芯片 客户难题: • 一行RTL改变导致640处 • netlist改变 • 几乎无法手工完成ECO 奇捷科技解决方案: • EasylogicECO生成的补丁只有其他商业工具的38%大小 • 防止局部密度(local density)过大导致增量 • 局部布局布线(Incremental P&R)难以完成 客户难题: • 工程师难以从门级电路中找到与RTL对应的信号 • 手工ECO极其困难 奇捷科技解决方案: EasylogicECO使用创新算法可以获得极佳ECO结果,补丁数量仅需6个,而竞品补丁数量超过200。(补丁数量越少越容易通过后续时序收敛。) 客户难题: 1.ECO 任务1 • 18个ECO 项目 • 修正39个模块 • 生成144个补丁单元 • 运行时间2191秒 2.ECO 任务2 (紧急任务,基于ECO任务1追加数个新的ECO项目) • 21个ECO项目 • 修正47个模块 • 生成220个补丁单元 • 运行时间2700秒 奇捷科技解决方案: • EasylogicECO可以解放工程师的ECO压力 • 使得工程师在宝贵的ECO窗口期发现并修正更多bug 客户难题: • 不同RTL可能产生截然不同的ECO结果,在进行ECO前难以预测哪种RTL是最佳修改方案 • 人工ECO费时费力,一般难以尝试多种不同的RTL修改方案 奇捷科技解决方案: • 通过EasylogicECO,工程师可以轻松尝试不同RTL修改方案的ECO结果,大大提高ECO成功率 团队介绍 本科和研究生攻读于清华大学计算机系EDA实验室,毕业后加入香港中文大学EDA实验室并取得博士学位,构建了公司旗舰产品EasylogicECO的核心算法和工具结构。 本科毕业于清华大学工程物理系和现代应用物理系。他有30年以上的销售和市场拓展经验,曾就职于新思(Synopsys)担任中国区销售副总经理,华大九天担任销售副总经理。其在任职期间,成功将华大九天的年销售额从百万级别增长到年收入过亿。 本科毕业于复旦大学计算机系,研究生攻读于清华大学计算机系EDA实验室,毕业后加入香港中文大学EDA实验室并取得博士学位,担任物理优化领域的产品开发负责人。 香港中文大学计算机系取得博士学位,在ECO优化中应用了逻辑综合、SAT和AI算法等独特技术以推动EasylogicECO的性能优势。他目前的研究领域之一是将AI的迷你神经网络框架应用于布尔逻辑以获得更好的ECO结果,这项开发结果将进一步加强Easy-Logic在工具算法方面的技术领先地位。 研究生毕业于香港中文大学工商管理学系和生命科学系。她曾就职于安永咨询、世界500强罗氏诊断和香港科技园企业创投基金,在风险管控和企业运营方面有超过10年的丰富经验。 本科就读于浙江大学,毕业后进入香港中文大学EDA实验室并取得研究生和博士学位。有超过10年的芯片设计和EDA行业的从业经验,曾管理上百人研发团队。 投票赢豪礼 方式1:识别上图海报二维码直接投票 方式2:点击“阅读原文”直接投票 10月30日 相约深圳 第五届硬核芯生态大会暨2023汽车芯片技术创新与应用论坛将于2023年10月30日举办,与您相约深圳国际会展中心(宝安新馆),直击新形势下中国芯的发展风口! 关于芯师爷-硬核芯年度活动 “芯师爷-硬核芯年度活动”是国内兼具创新性和影响力的评选活动,创办于2019年,迄今已成功举办四届,旨在发现、表彰优秀中国芯企业,提升中国芯企业在全球范围的影响力,并为企业联接电子终端工厂、高校院所及投资机构等合作伙伴,全面助力中国半导体产业发展。 关于芯师爷 芯师爷隶属于深圳市芯师爷科技有限公司,团队成立于2015年,是全球领先的产业社群和内容驱动型媒体,以输出产业优质内容为基础,提供客观、新锐、深度、及时的洞察,目前已形成半导体全产业链媒体矩阵:芯师爷、今日芯闻、全球物联网观察3大微信公众平台,组建有500多个主题的微信群。

相关文章

查看更多

>>

格创东智SEMICON SEA圆满收官,全栈CIM与工业AI智能体群赋能东南亚半导体智造跃升

CSPT&ITGV 2026 登陆无锡,汇聚全球智慧共探先进封装与玻璃基板新未来!

全域感知,一键部署:“星元智能体”开启国产AI落地新范式

发表评论 取消回复