-

当前位置:芯师爷

- 首页

- 热点资讯

(文:史悦)

2020,沧海横流,疫病横生,偏偏此时国际关系剑拔弩张。以中美摩擦为剧,一时间火花四溅,骇浪惊涛。

从中兴通信事件为始到516华为全面进入实体清单,此间已二年有余,中美关系逐步从长期的进出口互惠,走向科技领域的全面对抗。

尤其以半导体为首的科技产业被推入风口浪尖,甚至一个企业,便要承受一个国家的命运和担当。

作为产程密集度、工业自动化程度、技术密集度最高,代表人类最顶级智慧结晶的行业,半导体产业的低国产化、低自给化和产业中低端化,成为此次美国掣肘中国的利剑。

高端芯片不能自给,产业链环节缺失和结构倒挂,让中国的半导体产业成为此次中美对抗的阿喀琉斯之踵。

电子设计自动化—— Electronic Design Automation,简称EDA,是芯片设计最上游、壁垒最高的部分,却是国内芯片产业几乎最薄弱的环节,被强行推向舞台中央。

作为产业中枢和设计之母,EDA承载起中国半导体产业生态的塑造之路,其产业位置之重要,见微知著:

以设计自动化为题,EDA以计算机辅助设计(CAD)为桥梁,嫁接超大规模集成电路(VLSI)设计中所涉及的功能设计、综合、验证、物理结构(布线、布局和版图)等流程的全制;

以芯片设计生态为题,EDA发展的产业生态基础,嫁接了代工厂对于产业上下游的理解,培植高端芯片设计公司,是形成整套半导体系统生态的中枢神经;

以半导体生态为题,EDA作为半导体产业的发展杠杆,将会孕育整个半导体后摩尔时代的产业发展路径。以摩尔定律为代表的物理极限被打破,使得配套的设计工具和软件服务,决定了产业未来的发展路径和天花板。

集成电路作为整个半导体产业的核心,其技术设计的复杂性,产业结构的专业化,使得一套完整的EDA软件成为刚需,较之前有限的晶体管布局和布线难度,现有集成电路设计之繁杂,规模之巨大,均不是单纯人力范围所能覆盖。

EDA出现之前,传统设计人员必须通过手工完成设计和布线等基础工作,彼时前沿的工程师,不过是使用集合方法制造用于电路光绘的专用胶带(Photo plotter)便可满足需求。

EDA作为高阶的电子设计自动化,并未在彼时呼之欲出,取决于传统集成电路的复杂程度仍较原始,半导体工业仍延续粗放生产。

随着数据的快速扩张导致计算量的极限增长,手工设计愈发吃力。为了配合工程师的需求,自动完成掩膜草图开始出现,提供电路布局和布线的研发工具雨后春笋般出现在设计人员的视野中。

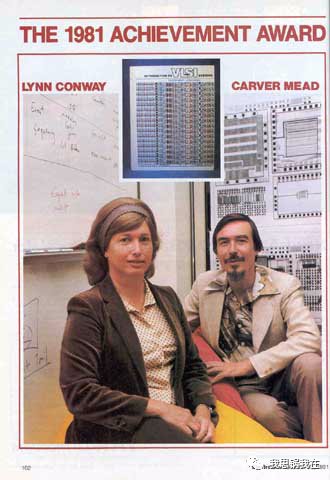

真正的突破出现在1980年,加州理工学院教授Carver Mead和全录帕洛阿尔托研究中心的程式设计师Lynn Conway共同发表了一篇具有划时代意义的论文《超大规模集成电路系统导论》 (Introduction to VLSI Systems)。

这篇论文将编程语言构建芯片设计的新思想推向世界。以此成果编写的《VLSI系统简介》成为当时标准的课堂教材,在超过一百所高校里使用。

(两位在1981年被Electronics期刊评为年度成就奖)

具体展开,EDA到底在芯片设计中扮演着怎样的重要角色?

芯片设计分为前端和后端,前端调节芯片逻辑,后端完成物理实现。

二者清晰划分但并不严格切分界限,涉及一切工艺相关则统一划分为后端,前端则对芯片门级网表电路进行逻辑梳理,一则实现对芯片的功能定义,二则为功能实现行为寻找物理路径,最终形成布局规划和逻辑输出。

芯片设计的过程,就是工程师利用程式码规划芯片功能的过程。而通过EDA工具,工程师得以将程式码转化成为实际电路设计。

再具体一点:

工程师向EDA提供完整的HDL code(Hardware Description Language,硬件描述语言代码);

EDA会根据逻辑闸设计图的规格对该代码进行修改和调整,生成功能正确的电路图;

最后供给后端进行布局模拟和电路制作,形成光罩,然后流片成产品。

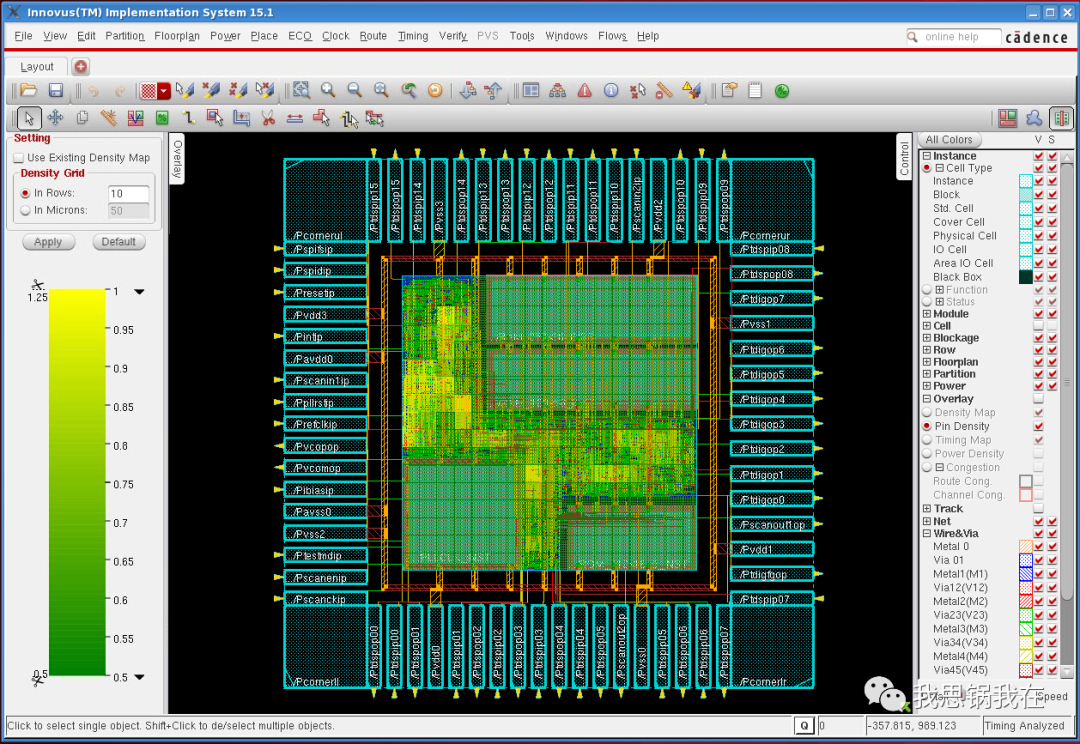

(EDA三巨头之一Cadence的产品界面展示)

作为逻辑综合工具的EDA,不仅为设计的逻辑闸提供意见的修改,其更重要的价值是在SoC(System on Chip,系统级芯片)数以亿计的今天,大幅度地降低了设计试错成本。

大规模集成电路的复杂度,已经远超人类设计仿真的控制极限。因此,在动辄流片费用百万千万计的今天,任何一家芯片公司都无法承受数次流片失败的成本。设计环节的丝毫差错,都可能导致巨大的财务损失。

EDA的出现,至少将此成本缩减超百倍。

随后,集成电路的布道者们开始大肆宣传集成电路与承载的人类命运,几乎和集成电路所能承载的复杂程度直接关联。这在当时看起来几乎荒诞的理论,在40年后的今天一语中的 ——

通过编程语言设计和验证电路预期行为,并通过逻辑综合工具软件得到低抽象级物理设计的研发途径,迄今为止仍然是数字集成电路设计的思想基础和工程基础。

在这个基础之上,EDA的商业化在上世纪80年代高速发展:

1981年,日后主宰全球EDA市场的三大巨头之一Mentor Graphics悄然诞生,日后名声飞扬的Xpedition、PADS、Mentor EE均诞生于此;

1986年,Gateway提出Verilog,这是迄今为止最流行的高级抽象语言;

同年,三巨头之二Synopsys诞生于美国加州Mountain View;

1987年,美国国防部资助的VHDL(Very-High-Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)问世,将设计实体分为内外部份,日后被广泛应用于机械工程、仪器科学和计算机科学中;

1988年,第三家巨头Cadence诞生在美国加州San Jose。

产业规模的急速扩张和竞争逐步加剧,导致分工模式进一步细化。

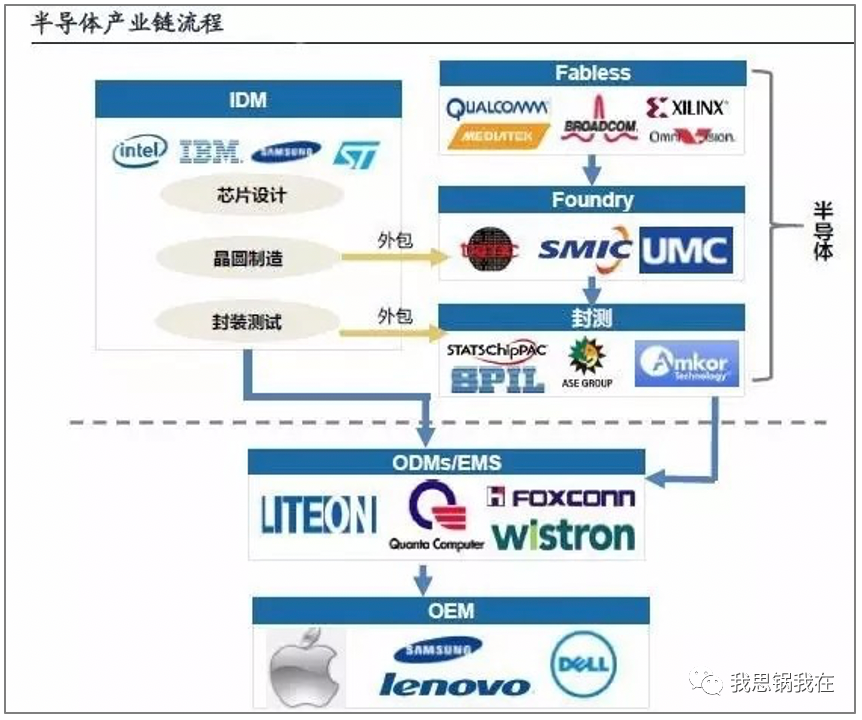

EDA犹如达摩克斯的利剑,精确切分原来由IDM (Integrated Device Manufacturer,集约化制造商)主导的半导体产业生态,逐步演化成了Fabless(无工厂仅设计) + Foundry(代工厂) + OSAT(Out Sourced Assembly and Testing,封测代工厂)的产业格局。

后来耳熟能详的IC设计、IC制造和IC封装,三大核心板块逐渐形成。

(来源:电子产品世界EEPW)

(来源:电子产品世界EEPW)

因为EDA,产业生态的上中下游,第一次被清晰的展现出来。

“当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。”

——戈登·摩尔(英特尔创始人之一)

摩尔定律作为半导体行业的金科玉律已运转多年,应验了无数半导体发展的重大时刻,并像圣经一般,收敛了整个芯片产业上下游的发展和演化规律,使其达到了实质意义上的统一。

而EDA的迭代,数年来也追随摩尔定律有序发展,承载了人类迄今为止超大规模集成电路的设计,发展和产业化演进。

但凡事终有极限,物理性征的限制,使得摩尔定律大有被替代更新的趋势。

在2019年人类撬开7nm大门后,传统EDA支撑下的IC设计遭遇瓶颈,对复杂设计的不断追求和提升集成电路性能,并缩小尺寸的要求进一步提升。

如何在EDA上追赶并超越摩尔定律,成为人类触碰下一代超大规模集成电路的核心要素 —— AI,物联网和虚拟现实等技术的不断更迭,人类对集成电路的要求也越发提升,对EDA的智能型要求也愈发提升。

以IT产业为例,手机和服务器为代表的设备更替周期从2010年全面到来至今年为止,人类社会对智能手机、大规模数据中心的替代基本结束。下一代智能终端包括和5G相关的各类硬件及软件工具将再一次带来设备更迭的产业浪潮。

(全球EDA市场区域分布,来源:Transparency)

因此,对集成电路的要求、设计复杂度的要求和可靠性的要求将更胜彼时,定制化、高个性化、私有化的要求也会随着产业周期的变革愈发高涨。

EDA工具除了设计,服务能力和智能化程度,必然会进一步划分EDA市场的终极格局和生态构成。

芯片设计所形成的重复使用设计模块,被称为我们常听到的IP(Intellectual Property,知识产权核)。

一个成功的IP设计往往拥有独家版权,并且将成为未来功能化芯片设计改良的母版,被各大公司采购和重复利用,造就了高通、英特尔等巨头。

并不是每个新的芯片都需要重复设计每个细节,各家公司可以通过购买成熟可靠的IP方案,在原有的IP基础上搭建特定的客户需求和技术方案,从而缩短设计开发流程,提高可靠性,将芯片的产业价值和规模最大化。

作为已经存在世间超过50年的传统型工业,集成电路工业已积累了数以万计的成熟IP供市场使用,现有的不少SoC厂商通过发掘市场中成熟的IP进行自我演进,并在功能上精确嫁接客户需求,缩短整个交付流程:

研发周期、交付周期和迭代周期同比例得到精简和优化,这个产业思路逐步扩大到各个SoC厂商成为固定套路,整合和发掘IP满足客户需求并大规模出货,成为厂商迅速实现规模化,集成化优势壁垒的通途。

在串联IP商业价值上,EDA为IP内核提供了三种表现形式:

HDL语言形式的加密软核。设计周期短,投入少且布线灵活,但后续工序与前序被切断,性能难以持续优化;

网表形式的固核。通过头文件或GUI(Graphical User Interface,图形用户接口)进行参数操作,收敛其他电路设计与该内核之间的接口;

版图形式的硬核。从掩膜出发,针对特定工艺进行功耗和尺寸的优化,不提供RTL(Register Transfer Level,寄存器转换级电路),因而更易于实现IP保护。

可以看出,三种特定的表现形式使得IP模块和芯片设计企业的研发体系高度耦合。

作为具备先发优势的欧美厂家,IP的丰富程度,与SoC企业的深度耦合经验和历史,让双方的竞争力成为一个密不可分的有效整体。

分立的EDA公司一枝独秀绝不能支撑整个体系,需要与系统级开发商深度耦合,系统级开放商对产业深度理解并挖掘客户需求,最终反馈到IP设计,再反向传导至EDA完成闭环。

不断的演进和替代,才能形成真正的生态和竞争模式。

EDA企业,SoC厂商,IP授权方深度和长期捆绑,最终决定了EDA产业赢家通吃的基本局面。新进者无论具备怎样密集和有效的设计基础和能力,都很难打破现有的产业格局。

(Intel的生态产业链)

不过如前面所述,随着科技发展和产业周期迭代,传统数字电路IP生产的方式方法,也在悄然发生改变。顶层架构设计和模块指标的模拟IP,如今已可自动生成和生产。自动IP的生成逐步成熟,使最优设计完全可以通过本身有效的数据收敛,得到理论上的最优解。

2018年,半导体IP市场规模约为46亿美元,而模拟IP自动生成领域,下穿到垂类行业(如射频、数模混合、处理器等)的话,当前基数均可忽略不计。

作为新兴行业,自动模拟IP生成工具的优化和产业化,未来将很可能成为EDA新的战场,跳过SoC形成的原有格局,在新格局上重新竞争,重新划分江湖。

想了解更多EDA公司最新资讯?

欢迎加入半导体信息服务VIP群!

EDA从无到有,并最终成为撬动整个半导体行业的杠杆和基石,前面提到的三大EDA厂商以江湖盟主的姿态,霸占产业山头。

提EDA,Synopsys就是不可逾越的大山,是EDA世界当之无愧的王者,行业制定者和领军人。在EDA的发展轨迹上,提供整体解决方案即Total solution,并从整体方案往下延展行业渠道的公司,往往更有竞争力 —— 犹如在半导体行业里掌握分立器件技术的公司比比皆是,但是捏合起来成为整体却艰难异常。

纵观美国半导体巨头发展简史,掌握Total solution能力的巨头,往往是从单一器件和单一能力入手切入市场,通过大规模的整合并购,完成自我能力的塑造和建设。

以Synopsys为例,34年的发展历史上,从幼年期收购Zycad公司的VHDL仿真业务入手,使得Synopsys一夜间掌握了前后端一体化的EDA能力,如此甜头在往后的岁月里被不断复制,加强,逐步衍生出全套的技术解决和工程验证能力,最终成为一代领军。

(位于美国加州山景城的Synopsys总部)

有意思的是,整合并购作为一种典型扩张手段,三大巨头具有明显的不同,这和企业本身的基因高度相关。

Synopsys从诞生初期便立足于为客户在整体上优化设计环境,核心Knowhow隐藏在产品后不让客户直接感知,产品迭代速度和发展,通过内部研发和交易并购解决。

从Astro、DFT到TetraMAX和Vera等产品来看,Synopsys力图从产品整体的角度,致力优化设计、布局到布线的整体环境,便于客户在设计流程的前期更加容易熟悉和感知环境,确保在时序和测试覆盖要求同时满足的情况下,尽可能提升操作体验,为客户的设计服务提供更自由的工具和交付空间。

Cadence从诞生的第一天便是高度混合的个体,前身SDA System和ECAD作为EDA江湖最早出现在公众视野的顶尖公司,擅长领域和对前后端理解有诸多不同,而二者最终于1988年合二为一,将Cadence瞬然保送至全球第一EDA企业的高度。

从程序方案服务和设计服务,覆盖从半导体、计算机系统、网络工程、消费电子及其他各类电子产品的设计,使其覆盖的产业和技术远超同类竞争对手,加上常年近40%的研发投入和美国国防部的长期支持,使得Cadence在2002年之前,一直处于全球EDA之巅。

Mentor Graphics的核心是EDA软硬件耦合,对PCB解决方案的设计上,提供EDA和模拟硬件系统。产业较前两家有一定差距,没有提供Total solution的能力,但PCB设计工具方案的完整度,使得该公司仍然稳居世界第三。

产业并购方面,MG自成立至今虽然也有66起并购发生,但产生行业影响力的事件并不多,最终在2016年11月以45亿美元卖身西门子,成为西门子数字工厂的一部分。

04

伴随中美对抗走入全新时局,半导体自给率将由主动替换走向被动替换,中国已是全球最大的半导体消费市场,据预测2020年将达到全球半导体消费总额的60%。

然而作为拥有超过86座光晶圆厂的超极半导体大国,却不得不面临国内EDA孱弱的现实:

EDA的自给化率却低于15%;

纯EDA国产化率低于5%,今年可能因为SoC工艺迭代而降至3%;

拥有全栈式技术路线,并大规模投入生产制造环节的公司小于5家。

严重的产业结构倒挂,既揭开了中国EDA发展的现实,也孕育了巨大的国内需求和替代机会。风险和机会并存,并将在未来的中国半导体生态中长期存在 ——

如果说半导体是中美贸易战中最被卡脖子的一个问题,那EDA的孱弱则是这个卡脖子问题中最核心之一。

历史上,EDA从诞生的第一天就进入欧美半导体产业体系被集中保护,从建国初期的“巴统”禁运(巴黎统筹委员会对中国实行禁运,国外EDA无法进入中国),到1988年打破封锁的熊猫系统横空出世,再到1994年巴统禁运取消,全球EDA产品全面进入中国。

国内EDA企业经历了早期探索,还未脱开襁褓却又迎来国外EDA的豺狼虎豹。随后市场的凋敝又带来研发费用不足和资本投入周转缓慢等连锁效应,造成了当前中国EDA发展缓慢,难以与三大巨头抗衡的局面。

一直到2008年国家核高基的鼓励扶持,以华大九天为首的中国EDA企业开始进入市场的主流视野。持续的技术投入、人才积累、与IP的有效粘连,也让一批企业从长尾客户切入,逐渐站稳脚跟。

同时,中国EDA市场的发展必然与本土半导体产业的发展息息相关。中国Fabless厂家已经占据全球四分之一的份额,原创IP逐步出现,急需一批提供与IP相关服务工具强粘连的服务商和渠道商。

因此作为承载熊猫系统等核心技术的华大九天,在国内被称为EDA的先行者,也是领先者。

尽管2009年公司才正式宣告成立,但从承载熊猫系统的技术、EDA和IP方面的积累,多次增资和更换股东,尤其大股东从华大集成电路到中国电子的转移,华大九天都拥有了在国内问鼎华山的实力和潜力。

从核心产品和已取得的成就上也可以看出:

模拟IC设计的全流程EDA系统国内唯一,也是全球四大模拟设计全流程平台,仿真技术可支持7 nm工艺,出货量过百亿,SKU达到数百款;

数字SoC设计优化EDA,覆盖国内90%以上企业,已基本完成国产化替代;

晶圆制造专用工具,掩膜板处理软件全球第一;

平板设计EDA全球唯一,国内新建产线超过半数都采用该系统。

华大九天的发展基调也定位在垂类行业的Total solution上,例如在数字SoC设计优化的EDA领域,已经形成从标准单元库特征化、工艺资料分析检验、规则检车时钟分析、到一站式版图分析集成逐一击破的整体能力。

就像前面所述,EDA的发展并非孤岛,华大九天最大的优势便是中国半导体的海量市场支撑。

尽管产业上下游从当下来看,大多并不具备高端器件的生产及整合能力,但巨大的市场潜力和需求、日趋动荡的中美关系,加上EDA本身特殊的产业位置,都催生华大九天继续深入产业上下游,做好整个IC设计的母版和粘合剂。

其次,中国的人工智能产业发展,通信射频、汽车电子、MEMS(微机电系统)等各领域资本的疯狂布局,一定会催生以国产化替代为主的EDA浪潮,这个浪潮的核心是通过产业下游催生产业上游的国产化改良和产业流程的再造。

对中低端开发厂商而言,具备定制化能力提供IP和EDA软件授权的企业大有人在,急需专业EDA技术支持进行设计整合。

同样,提供集成器件设计和集成能力的制造商虽为数众多,但下游场景从之前的工业自动化、电子、航空航天等领域,早已渗透到消费级电子产品、通信领域的基站和设备、高性能服务器及计算存储单元。

一切都在倒逼国内EDA设计企业提供具有中国特色的电路分析服务和设计服务。

除了华大九天,广立微电子,今年5月申报科创板的芯愿景,还有创业公司中的蓝海微科技、博达微科技、奥卡思微电子等等,也通过器件建模、PDK(Process Design Kit,工艺设计包)验证、形式验证等产品,为半导体企业提供除去主体设计外的集成电路工艺设计包、半导体参数测试和器件验证等全流程的服务工具。

05

无论是暂时领先的华大九天,还是即将登陆资本市场的芯愿景或早期公司,想要在本轮市场浪潮中获得有效机会并赶超巨头,可能需要具备以下三个条件:

打信息差:产品矩阵模仿国外三大巨头意义不大,基于中国IC设计市场提供定制化方案,势必要打三大巨头在中国半导体生态中的信息差;

人才为王:充分利用此时半导体市场的集中火爆,用最大的可能性吸收EDA核心人才,重塑人才梯队,半导体的核心竞争永远是人才稀缺性;

共建生态:EDA的发展绝不是孤立存在,客户替代意愿只能归为强制替代而不是市场化行为,EDA本身的工作远没有建立一个共荣的生态重要。

2020年,作为半导体设计之母的EDA,从最初的高深莫测,裹挟着焦虑和民族情绪,终于走到时代的中央。

在全球疫病当前的今天,中国半导体市场伴随着资本和政策的簇拥,如火如荼。这份火热既有市场对于沉寂多年的高科技的确定性补偿,更多则体现出民族对于攻破半导体枷锁的信心,甚至信仰:

一个强大的中国,一定要拥有一颗强大的中国芯。

EDA的中场战事,才刚刚开始。

-End-

本文转载自微信公众号我思锅我在,作者史悦,供交流学习之用。如有任何疑问,敬请与我们联系info@gsi24.com。

推荐关注:全球物联网观察

微信号:gsi24-iot

您的物联网中央情报局!

相关文章

查看更多

>>

格创东智SEMICON SEA圆满收官,全栈CIM与工业AI智能体群赋能东南亚半导体智造跃升

CSPT&ITGV 2026 登陆无锡,汇聚全球智慧共探先进封装与玻璃基板新未来!

全域感知,一键部署:“星元智能体”开启国产AI落地新范式

发表评论 取消回复