-

当前位置:芯师爷

- 首页

- 热点资讯

近期的热门话题离不开芯片的短缺和各国政府对半导体行业的大力投资。半导体行业迎来了复兴,产业链上的各个环节有哪些契机?

华美半导体协会夏季研讨会”A Renaissance for Semiconductors”将于美西时间7月24日周六下午2点至6点(中国时间7月25日周日上午5点至9点)线上举行。多位重量嘉宾将分享精彩观点,包括MIT教授以及OpenHW, ARM, Cadence, NXP, SEMIFIVE, Facebook, SmartGiant, Macronix, proteanTecs多位高管。

免费早鸟票报名时间有限,注册请访问:

http://www.caspa.com/events/symposium/event-list/60dd499655b9535728b103cf

扫码参会

2021 Summer Symposium Speaker Information

Rick O'Connor

President and CEO at OpenHW Group

Bio:

Rick O'Connor is Founder and serves as President & CEO of the OpenHW Group a not-for-profit, global organization driven by its members and individual contributors where HW and SW designers collaborate in the development of open-source cores, related IP, tools and SW such as the CORE-V Family of open- source RISC-V cores. Previously Rick was Executive Director of the RISC-V Foundation which was launched by Rick in 2015. Today, under RISC-V International, the RISC-V ecosystem consists of more than 400 members building an open, collaborative community of software and hardware innovators powering processor innovation. With many years of Executive level management experience in semiconductor and systems companies, Rick possesses a unique combination of business and technical skills and over Rick’s career, he was responsible for the development of dozens of products accounting for over $750 million in revenue. Rick holds an Executive MBA degree from the University of Ottawa, Canada and is an honors graduate of the faculty of Electronics Engineering Technology at Algonquin College, Canada.

Speech Title: CORE-V: Industrial Grade Open-Source RISC-V Cores

Abstract:

The CORE-V family is an OpenHW Group project to develop, deploy, and execute pre-silicon functional verification and SoC based development kits of the CORE-V family of open-source RISC-V cores. Written in SystemVerilog, the CORE-V open-source IP matches the quality of IP offered by established commercial providers and is verified with state-of-the-art, auditable flows.

CORE-V cores are verified using CORE-V-VERIF a silicon-proven, industrial-grade functional verification platform. CORE-V-VERIF has been used to execute a complete verification cycle of the CORE-V CVE4 (CV32E40P 4-stage embedded class core) and is currently being used to execute verification of additional CVE4 variants as well as CVA6 32 and 64bit 6-stage embedded class cores. CORE-V-VERIF leverage verification components developed by the RISC-V community and will be continuously maintained and enhanced to integrate the latest best-practices and technology for the verification of future CORE-V cores such that CORE-V cores can be used in high-volume production SoCs.

Chloe Jian Ma

Vice President, China GTM, IOT & Embedded, Arm

Bio:

Chloe Jian Ma is VP of China Go-To-Market for the IOT and Embedded Line of Business at Arm. In this role, Chloe is responsible for strengthening and expanding Arm products, solutions and ecosystem for China market so that the next wave of innovations in AIoT and embedded intelligence happen on Arm platform. She joined Arm from the RISC-V world, where she worked for both SiFive and StarFive (SiFive’s China JV) and had her hands full with many aspects of the business from global technology partnership/ecosystem building, to GTM strategy, to fundraising and running a regional subsidiary. Chloe’s experience in semiconductor industry also included Mellanox and Intel, where she led the GTM of cloud networking and compute solutions into the hyperscale Internet and Cloud service provider segment. Prior to entering the semiconductor industry, Chloe assumed engineering and marketing leadership roles in the networking industry at Juniper Networks, Huawei and Cisco Systems. To close the full loop, her 1st job was with Wind River in real-time embedded OS with a vision to make everything smart! Chloe received an MBA degree from Wharton, an MSEE from University of Southern California, and a BS in Electronics from Peking University in China.

Speech Title: Embrace Edge Native Computing in the AIoT Era

Abstract:

What used to be a device to make phone calls has turned into an information hub that can see, hear, sense, and connected us to the world. The mobile cloud era has nurtured a slew of great companies such as Apple, Google, Amazon, etc. as well as pushing Arm to the stardom as the de facto architecture for smart mobile devices.

Yet we are transitioning into a new Edge Intelligence computing era post mobile cloud that is signified by the combination of Artificial Intelligence and Internet of Things, the AIoT Era. In this era, what has happened to mobile phones and more will happen to everything else, cars, shops, home appliances, factories, and they can also have capabilities to hear, see, sense and make intelligent decisions with the information gathered from real world. The AIoT era will transform every industry and along with that, democratize technologies to everyone so that we can all innovate without a PhD in computer science.

The semiconductor industry is experiencing a renaissance and is standing in the forefront in defining the AIoT era, where cloud native computing will need to evolve into edge native computing. In this session, Chloe Jian Ma from Arm will walk you through the key technology trends in edge computing and explain why we need to embrace edge native computing.

Rishi Chugh

VP of Marketing, Cadence Design Systems

Bio:

As VP of Marketing , Rishi Chugh heads the IP division of Cadence Design, responsible for interface IP (Memories & SerDes) as well as Analog Mixed Signal business. Prior to joining Cadence, Mr. Chugh held Sr. Director role at Cavium, managing their Data Center Processor division and was responsible for the ARM server product line. Prior, Mr. Chugh has held Product Marketing role at Broadcom’s Data Center switch product line managing the Trident switch product line. Mr. Chugh has over 20 years of industry experience working at Cavium, Broadcom, Altera, LSI and Artisan Components (acquired by ARM). Mr. Chugh holds a Bachelor of Electronics degree from the University of Bombay in India, a Master’s of Science degree in Electrical Engineering from San Jose State University and an MBA from Santa Clara University.

Song Han

Assistant Professor, MIT EECS

Bio:

Song Han is an assistant professor at MIT’s EECS. He received his PhD degree from Stanford University. His research focuses on efficient deep learning computing. He proposed “deep compression” technique that can reduce neural network size by an order of magnitude without losing accuracy, and the hardware implementation “efficient inference engine” that first exploited pruning and weight sparsity in deep learning accelerators. His team’s work on hardware-aware neural architecture search that bring deep learning to IoT devices was highlighted by MIT News, Wired, Qualcomm News, VentureBeat, IEEE Spectrum, integrated in PyTorch and AutoGluon, and received many low-power computer vision contest awards in flagship AI conferences (CVPR’19, ICCV’19 and NeurIPS’19). Song received Best Paper awards at ICLR’16 and FPGA’17, Amazon Machine Learning Research Award, SONY Faculty Award, Facebook Faculty Award, NVIDIA Academic Partnership Award. Song was named “35 Innovators Under 35” by MIT Technology Review for his contribution on “deep compression” technique that “lets powerful artificial intelligence (AI) programs run more efficiently on low-power mobile devices.” Song received the NSF CAREER Award for “efficient algorithms and hardware for accelerated machine learning” and the IEEE “AIs 10 to Watch: The Future of AI” award.

Speech Title: TinyML and Efficient Deep Learning with Limited Silicon Resource

Abstract:

As there’s a global shortage of silicon chips, it is crucial to enable deep learning on resource-constrained devices. I will describe model compression techniques including pruning and quantization to reduce the model size, then AutoML and hardware-aware neural architecture search techniques to synthesize small and compact neural networks given latency/memory constraints, which enables Imagenet classification on a microcontroller that has only 1MB of Flash. Finally I’ll describe co-designing deep learning accelerator architecture together with the neural network topology. I will conclude by discussing the efficient techniques for various deep learning applications.

Shelly Van Dyke , NXP

VP & head of Strategy Automotive Processing business and the Automotive segment, NXP

Shelly Van Dyke is VP & head of Strategy for NXP’s Automotive Processing business and the Automotive segment. She has over 30 years of experience in engineering, strategy and strategic finance for the semiconductor industry and the technology supply chain, particularly in automotive and industrial segments. Career highlights include the start-up of the first Motorola 200mm fab, Freescale’s two Initial Public Offerings, serving on the Board of the World Semiconductor Trade Statistics industry association, the NXP-Freescale merger integration, and chartering the Financial Planning & Analysis department at National Instruments. She has a Bachelor’s degree in Chemical Engineering from UT Austin, and a Master’s in Business Administration from Regis University, and lives in Austin, Texas.

Ho Wai Wong-Lam林可蕙램호와이

VP Strategy, NXP Semiconductors

Ho Wai is a technology and semiconductor veteran for 30+ years. She started with Philips Research in The Netherlands, and moved to US to join Philips Semiconductors, which became NXP Semiconductors. She has worked in a wide range of disciplines, from research to R&D, from engineering management to marketing and business development, and since 2013 in strategy. In her role as VP strategy, she supports the analog, power and interface strategy development at NXP, which spans a wide range of applications including automotive, mobile, and computing. Since 2020, she represents NXP as a sponsor and a volunteer judge at Extreme Technology Competition (XTC) which is a worldwide competition for startup companies in the theme of “Technology for Good”.

Ho Wai graduated in Electrical Engineering from the University of Hong Kong, and got her master’s degree in Eindhoven, The Netherlands, through a Philips scholarship. She is (co-)author of 13 granted patents, and a dozen peer-reviewed journal papers. Ho Wai is an engineer at heart and a strategist by profession. She is a team player, team leader and a team builder. She believes in Tech for Good - doing well while doing good.

Speech Title: Accelerating the future of mobility with new vehicle architectures and electrification

Abstract:

New vehicle applications are driving growth in the automotive semiconductor market. Applications like safe driving with radar solutions, electrification with battery management systems, and cloud connectivity with data analytics, have brought new requirements and challenges for the automotive industry. To support these new applications more and more functionality has been added to the vehicle, which means massive growth in content and complexity. For example, to be successful in the electric vehicle market, carmakers need to continuously drive battery cost down, extend drive range, lower charge time, electrify entire fleet with platform concept and reuse across models, and predict maintenance for battery safety. Vehicle architectures need to evolve to support all the new requirements: simplify software integration, enhance networking capabilities, reduce vehicle weight, and optimize costs – all of this, while guaranteeing the highest levels of auto-grade quality, system-level functional safety, security and reliability.

The first architectural evolution will support a smarter, software defined vehicle where data can be shared as needed, optimizing cross domain applications so that functions can be moved up to the software for faster updating/rollout of new features and more integration in the electronics systems. The second evolution focuses on zonal control to simplify the vehicle’s network to re-organize electronics toward modularity and scalability dramatically reducing wire routing, costs, and weight. This session will introduce these key innovation areas and outline the implications for future vehicles.

Panelists:

Moderator

Wiiliam Kou

Director of Sales

proteanTecs

Ho Wai Wong-Lam林可蕙램호와이

VP Strategy,

NXP Semiconductors

Kelvin Low

General Manager, SEMIFIVE US Inc

Bio:

Kelvin Low joined SEMIFIVE as the General Manager of SEMIFIVE US Inc with broad-ranging experience in various silicon foundries and design ecosystem. Mr. Low is responsible for SEMIFIVE US Inc’s operations and business expansion, which includes Sales, Business Development, Field Technical Support and Program Management functions. He is also responsible to extend SEMIFIVE’s business reach to other worldwide regions.

Prior to SEMIFIVE, Mr. Low held key Technical, Marketing and Sales executive positions at Arm Inc, Samsung Foundry and GLOBALFOUNDRIES. He was also recently the vice president of marketing, strategy and overseas sales at SMIC. Mr. Low started his career at Chartered Semiconductor Manufacturing as a process integration engineer where he led development of logic, mixed signal, RF, CIS and NVM processes. Mr. Low also had additional responsibilities as the marketing lead in the IBM joint development alliance and Common Platform.

Mr. Low received his bachelor’s degree in electronics and electrical engineering with First Class Honors from the National University of Singapore.

Title: Rise of Custom Silicon

Abstract:

Many have debated that the slow down or even demise of Moore’s Law is inhibiting new product innovations. But we continue to enjoy new product introductions and the need to innovate and customize is even more crucial than ever in this highly competitive market. Domain specific design solutions is one of the key enablers. SEMIFIVE will share the latest trends and discuss different approaches to realize your product ideas to silicon.

Jeremy Chen

Engineering Manager at Facebook FRL

Bio:

Jeremy Chen leads one of the Systems EE Teams inside FRL, responsible for Product Key Technology Development and New Technology Introduction, and oversees the product line's Technology Roadmap.

In his previous role with Apple, he served as Power Management IC Architect and Power/Analog lead for iPhone Team.

Jeremy has years of experience leading custom silicon definition, development, and integration for some of the world's most popular and successful consumer products. He also has a deep understanding of SiP Technology and Harsh Environment Electronics design based on previous experience in the Oil & Gas Industry.

Jeremy holds a master's degree in Electrical and Computer engineering from Texas A&M University and a bachelor's degree in Electrical Engineering from Zhejiang University.

Ian Wang

Technology Director, SmartGiant Technology Co. Ltd.

Bio:

Mr. Ian Wang has 22 years of experience in semiconductor industry. He is currently Technology Director and Marketing Manager at SmartGiant Technology Corporation Limited in Santa Clara, California, USA. Prior to SmartGiant, he was an Engineering Manager at Intel Programmable Solutions Group (PSG) in the field of FPGA Design Verification. Before Intel, he worked as design engineer for Alcatel-Lucent Inc. in the field of ASIC design.

Mr. Wang received a Master of Electrical Engineering degree from Carleton University and a Master of Science in Physics from McGill University, both in Canada. He also earned his Bachelor of Science in Physics from Nanjing University in China.

Mr. Wang served as a member of the Board of Directors for CASPA since 2017. He acted as the Head of Publication in 2018, and the Head of Symposiums in 2019 and 2021. Mr. Wang has multiple scientific publications in Physics and Microelectronics. He served as a Technical Paper Reviewer for IEEE Transactions on Circuits and Systems II.

Jim Yastic

Director of Technical Marketing, Macronix

Bio:

Jim Yastic is a Technical Marketing Director at Macronix, responsible for ecosystem, market, product, and business development. With 30 years of experience in the high technology sector, his previous roles include engineering, product marketing management, and business development for organizations focused on semiconductor, communications, and embedded software markets. Jim holds a MBA degree from St. Edwards University in Austin, and a BSEET and Computer Science degree from Chapman University in Orange CA.

相关文章

查看更多

>>

34万㎡三展联动协同共筑芯生态,IC创新博览会9月深圳举办

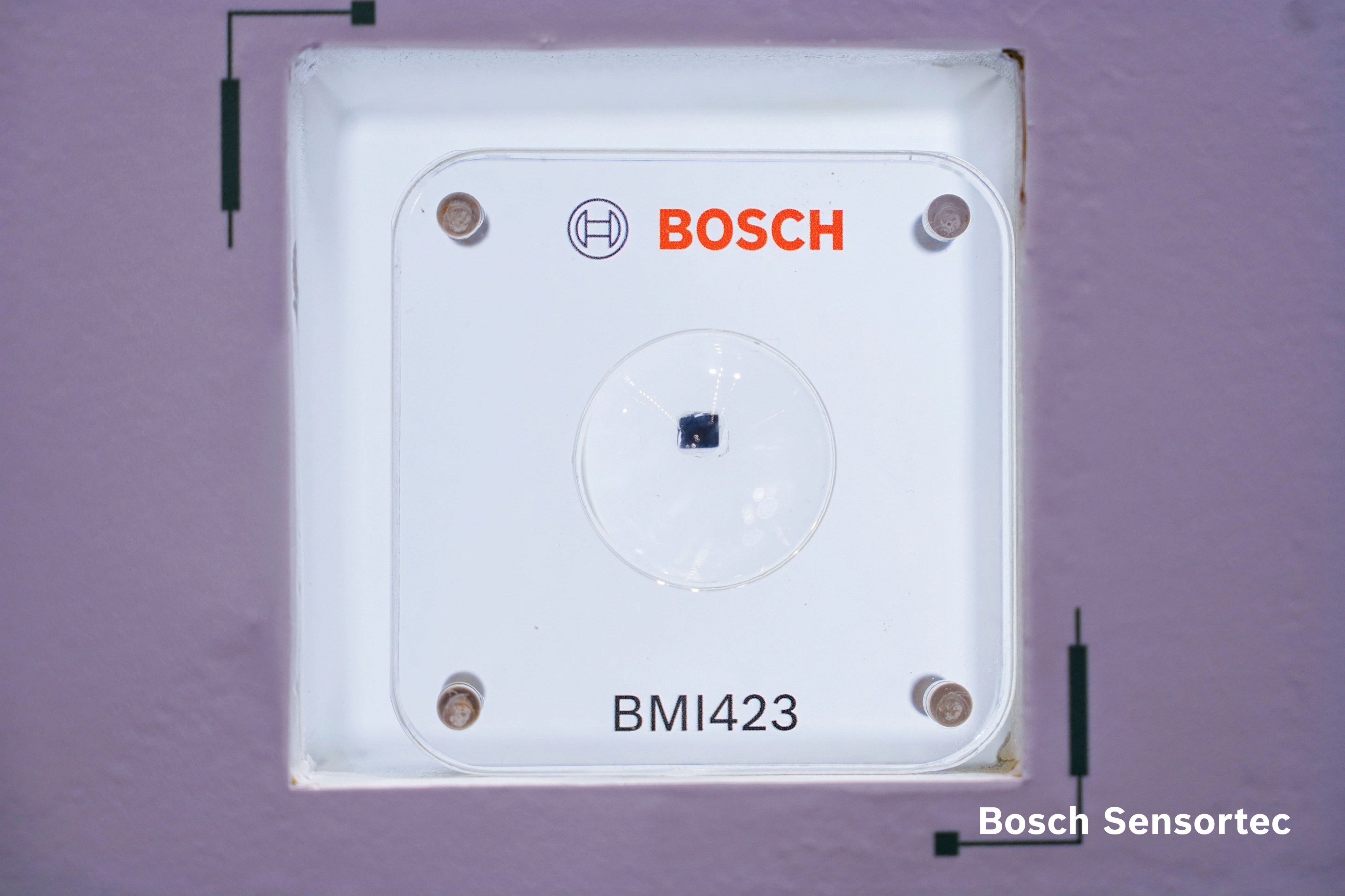

本该在云端的AI,现在“住”进了传感器里

地平线完整战略拼图落子:芯片+OS+智驾,剑指整车智能体第一载体

发表评论 取消回复